Компания SiFive объявила о выпуске своих новых ядер E2 IP серии с низким энергопотреблением, маломощных ядер микроконтроллера, разработанных для использования во встроенных устройствах. В настоящее время в состав нового семейства входят два ядра:

- E21, ядро обеспечивающее основную производительность для микроконтроллеров, слияние датчиков, и предназначенное для рынков интеллектуальных IoT

- E20, стандартное ядро SiFive с низким энергопотреблением, предназначенное для микроконтроллеров, IoT, аналогового смешанного сигнала и приложений с конечным автоматом

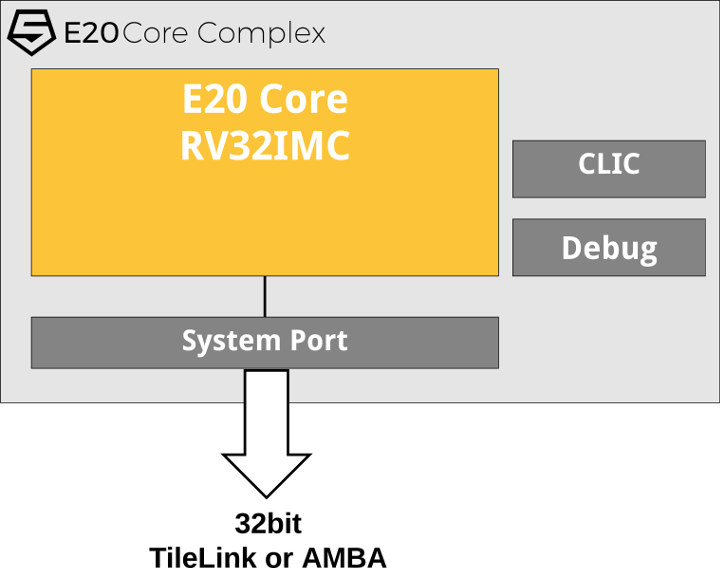

SiFive E20 MCU ядро

Основные характеристики основного IP-ключа SiFive E20:

- RISC-V ISA — RV32IMC

- Только машинный режим

- Двухступенчатый пайплайн

- Системный порт для доступа к внешней памяти

- Core Local Interrupt Controller (CLIC) с 32 прерываниями

- Расширенная отладка с 4 аппаратными точками останова/точками наблюдения

- Производительность — 1.1 DMIPS/МГц; 2.4 CoreMark/МГц

- Мощность/Диапазон частот/Ареал

- 28 нм HPC — 0,58 мВт; 725 МГц и выше; 0,023 мм2

- 55 нм ЛП — 1,3 мВт; 250 МГц и выше; 0,064 мм2

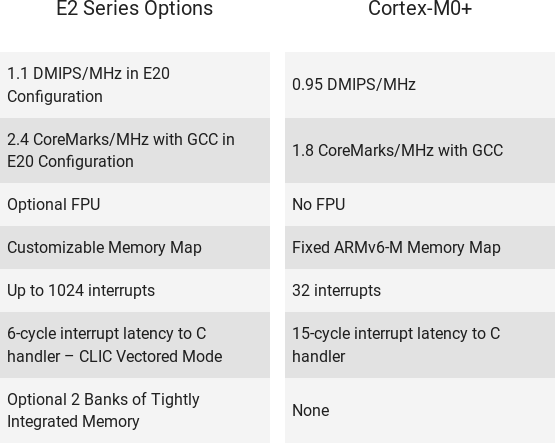

Сравнительные характеристики ядра E20 и ядра Arm Cortex-M0 +, предоставленные компанией, показаны в таблице ниже.

Исходя из данных таблицы, фаворит — ядро E20, но, возможно, стоит упомянуть, что сравнение энергопотребления отсутствует, хотя E20 может работать больше на МГц. На странице Cortex M0 + упоминается, что “Cortex-M0 + достигает потребляемой мощности ниже 4 мкВт/МГц (процесс 40LP, базовая конфигурация) при достижении производительности 2,46 CoreMark/МГц”, что отличается от числа, представленного в таблице, хотя данные SiFive получены с помощью тестов GCC, поэтому это не только теоретическое число.

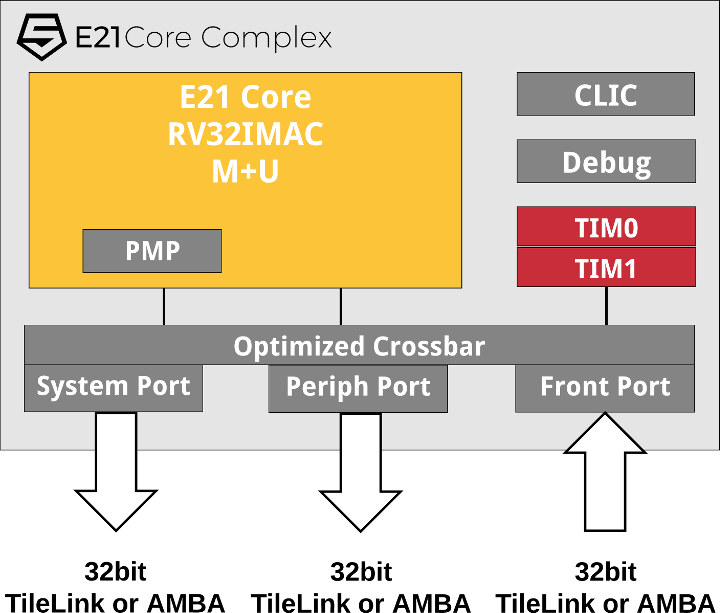

SiFive E21 MCU ядро

Основные характеристики SiFive E21 Standard Core IP :

- RISC-V ISA — RV32IMAC

- Машинный и пользовательский режимы с 4-мя областями Physical Memory Protection

- Трехступенчатый пайплайн с одновременным доступом к инструкциям и данным

- 2 банка плотно интегрированной памяти

- Системный, периферийный и фронтальный порты

- Контроллер прерываний CLIC с 127 прерываниями

- Расширенная отладка с 4 аппаратными точками останова/точками наблюдения

- Производительность — 1,38 DMIPS/МГц; 3.1 CoreMark/МГц

- Мощность/Диапазон частот/Ареал

- 28 нм HPC — 1,3 мВт; 585 МГц и выше; 0,037 мм2

- 55 нм LP — 3,1 мВт; 210 МГц и выше; 0,1 мм2

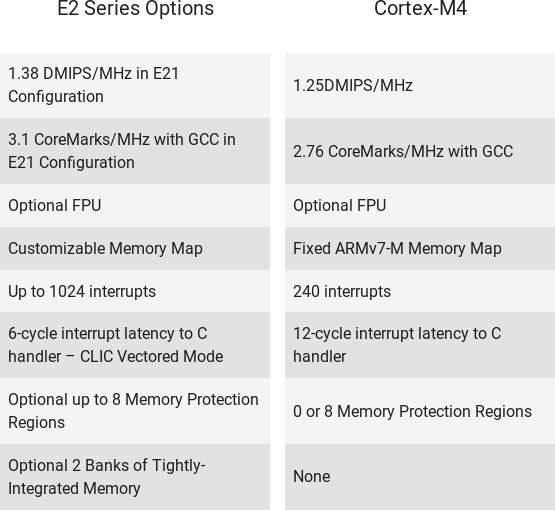

Сравнение ядра SiFive E21 с ядром Cortex M4.

То же самое относится и к этой таблице.

Компания SiFive предоставляет оба ядра RISC-V Core IP в Verilog, данные тестирования, комплект для разработки программного обеспечения, руководство пользователя, посвященное интеграции, синтезу и ограничениям.

Более подробную информацию вы найдете на странице SiFive E2 series, где вы также можете скачать битовый поток FPGA для оценочного набора Digilent Arty A7-35T на базе Artix-7 и/или запросить оценку RTL.

Выражаем свою благодарность источнику с которого взята и переведена статья, сайту cnx-software.com.

Оригинал статьи вы можете прочитать здесь.