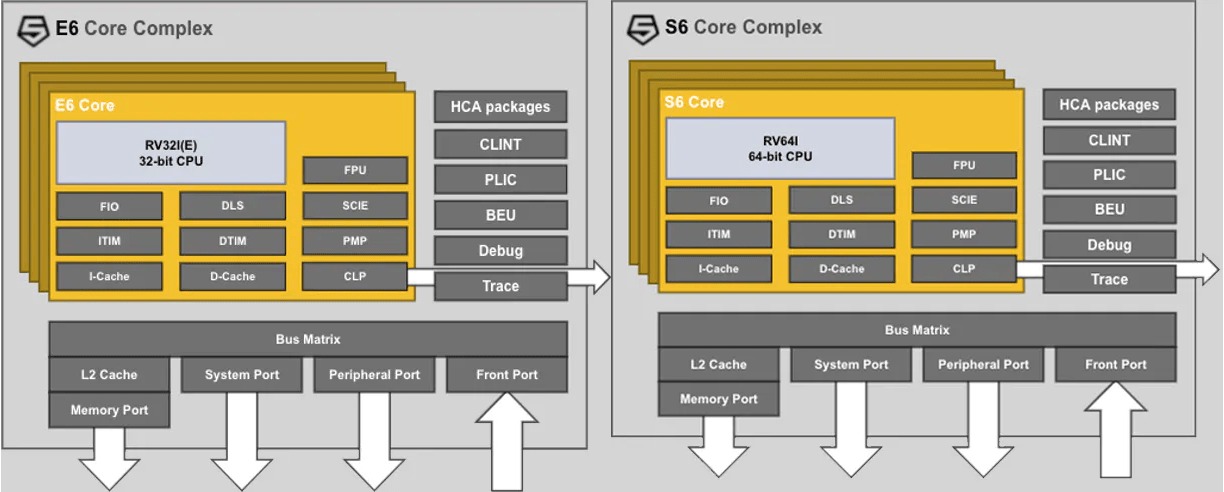

Всего через несколько дней после анонса SiFive Performance P650 компания SiFive анонсировала семейство процессоров SiFive Essential 6-Series RISC-V, включающее четыре 64-битных/32-битных ядра реального времени и два ядра приложений с поддержкой Linux, а также SiFive 21G3 с различными улучшениями существующих семейств.

Читать далее «Процессоры Sifive Essential 6-Series RISC-V нацелены на Linux и приложения реального времени»Ядро SiFive Performance P650 RISC-V превосходит Arm Cortex-A77 по производительности на мм2

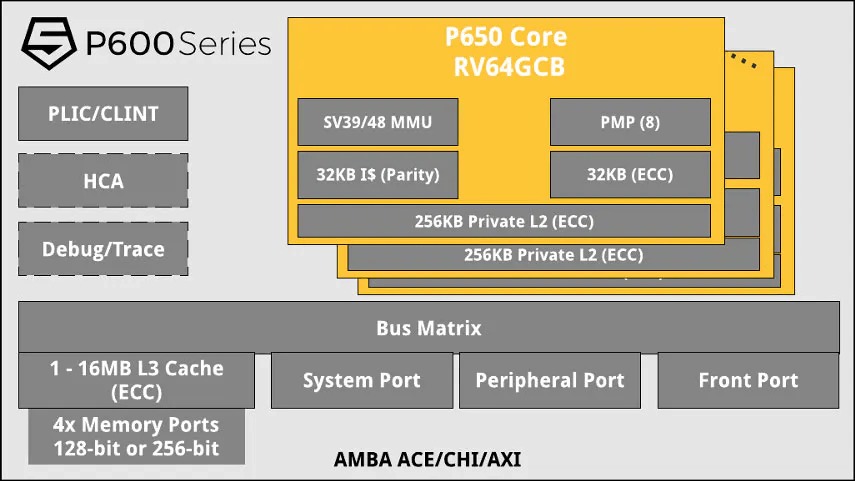

Около шести месяцев прошло с тех пор SiFive анонса Performance P550 «быстрый 64-битный RISC-V процессор», и теперь компания представила еще более быстрый RISC-V ядро с Performance P650, который, как ожидается, соответствует производительности Cortex-A77.

Читать далее «Ядро SiFive Performance P650 RISC-V превосходит Arm Cortex-A77 по производительности на мм2»Ubuntu 20.04/21.04 64-разрядная версия RISC-V выпущена для плат QEMU и HiFive

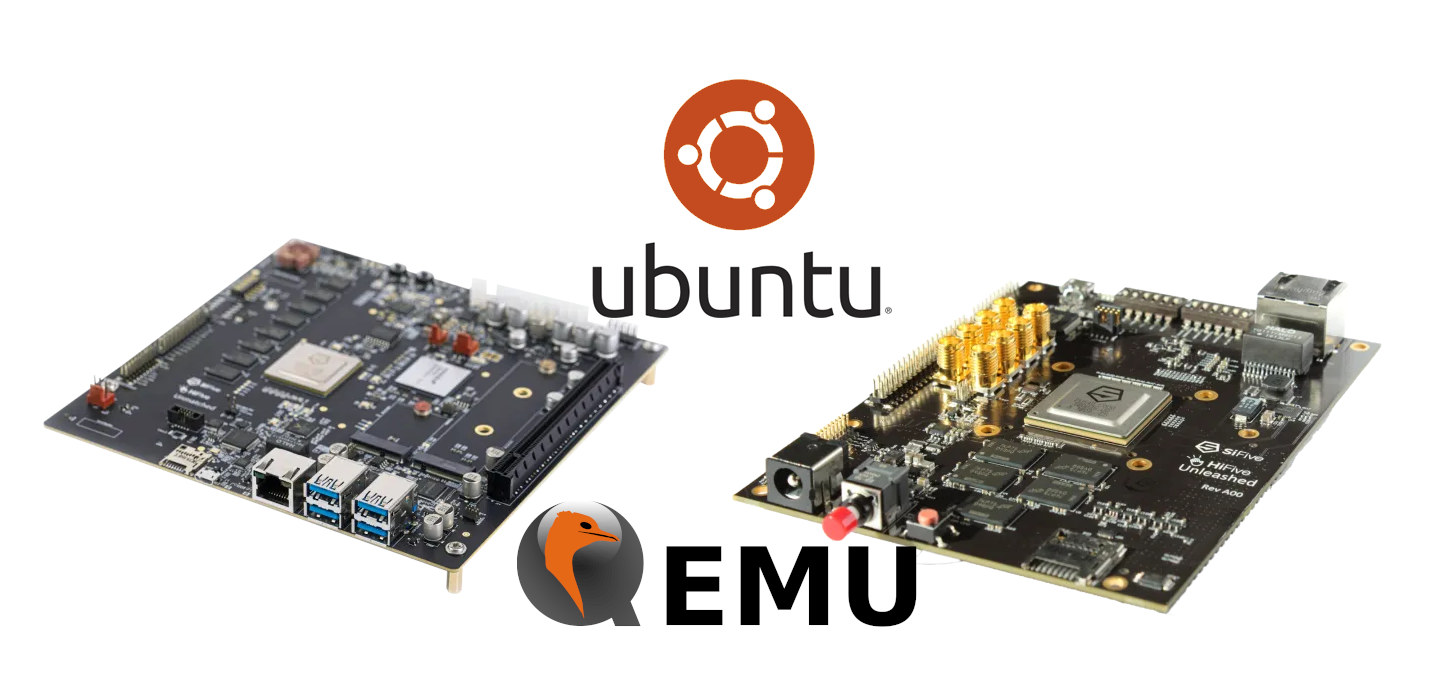

Открытая архитектура RISC-V воодушевляет, но еще предстоит проделать большую работу, чтобы довести экосистему до уровня Arm или архитектуры x86, от кремния до программного обеспечения. Прогресс осуществляется поэтапно, и одним из этих шагов – выпуск Canonical 64-битных образов RISC-V (RISCV64) Ubuntu для некоторых плат SiFive HiFive, а также эмулятора QEMU с открытым исходным кодом.

Читать далее «Ubuntu 20.04/21.04 64-разрядная версия RISC-V выпущена для плат QEMU и HiFive»SiFive Performance P550 – на сегодняшний день самый быстрый 64-битный процессор RISC-V

SiFive анонсировала два ядра RISC-V «Performance». Performance P550 – на данный момент, должен быть самым быстрым 64-разрядным процессором RISC-V с показателем SPECInt 2006 8,65/ГГц, а также процессор с поддержкой Linux – Performance P270 с полной поддержкой векторного расширения RISC-V v1.0 rc.

Читать далее «SiFive Performance P550 – на сегодняшний день самый быстрый 64-битный процессор RISC-V»RISC-V International раздаст 1000 плат для разработки с архитектурой RISC-V

Лучший способ получить хорошую поддержку программного обеспечения для новой платформы – передать оборудование в руки разработчиков. Именно это и делает RISC-V International, приглашая разработчиков заполнить заявку на плату разработчиков с архитектурой RISC-V, спонсируемую RISC-V и участвующими членами.

Читать далее «RISC-V International раздаст 1000 плат для разработки с архитектурой RISC-V»64-разрядный процессор SiFive Intelligence X280 RISC-V обеспечивает ускорение нагрузок искусственного интеллекта

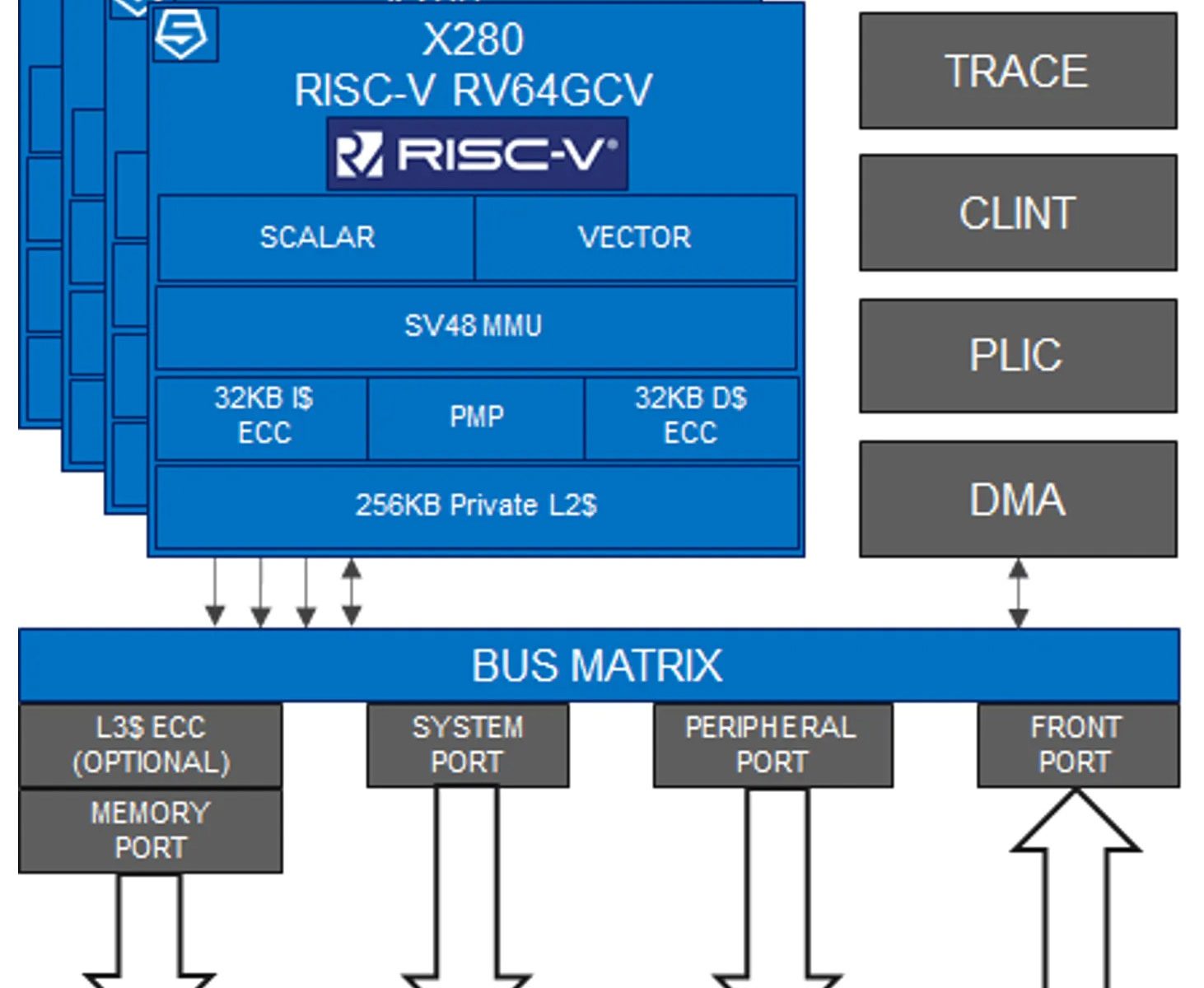

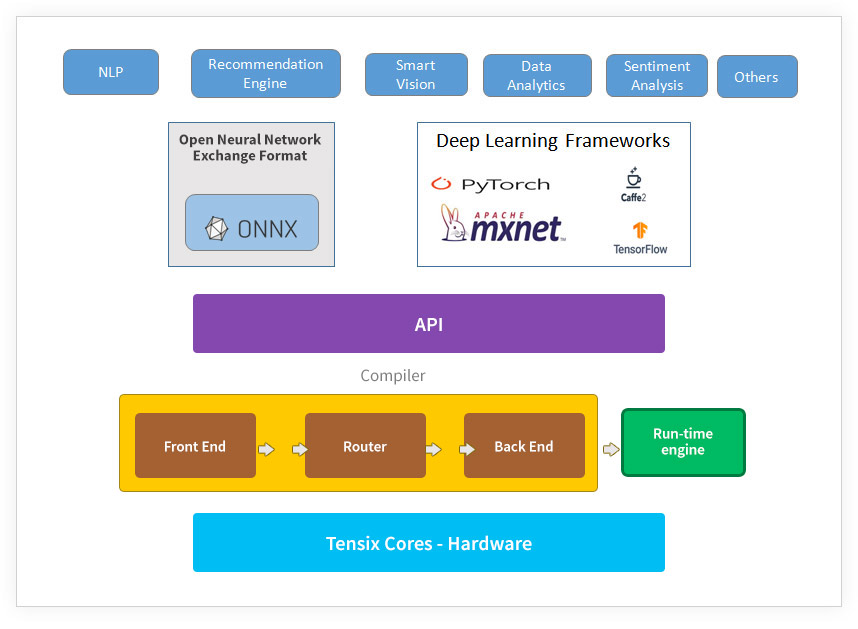

Последним ядром RISC-V, объявленным SiFive, было IP-ядро RISC-V серии U8, которое нацелено на конкуренцию с ядром Arm Cortex-A72. Но в своем последнем анонсе компания представила многоядерный процессор с архитектурой RISC-V – SiFive Intelligence X280 с 64-разрядным ядром U7 серии RISC-V, поддерживающий Linux, с добавлением векторных расширений и расширения SiFive Intelligence Extensions, а также оптимизированный для вычислений AI/ML.

Читать далее «64-разрядный процессор SiFive Intelligence X280 RISC-V обеспечивает ускорение нагрузок искусственного интеллекта»Платформа SiFive Intelligence, используемая Tenstorrent и Renesas

SiFive объявила, что стартап Tenstorrent, занимающийся микросхемой искусственного интеллекта, лицензирует новый 64-битный процессор SiFive Intelligence X280 для своих ядер Tensix, а Renesas будет использовать SiFive Intelligence для своих автомобильных процессоров.

Читать далее «Платформа SiFive Intelligence, используемая Tenstorrent и Renesas»Выпуск SiFive Core IP 21G1 улучшает обработку битов, модуль с плавающей запятой, уменьшает объем кода

Поскольку SiFive имеет ряд ядер с архитектурой RISC-V от маломощных E2-серии до высокопроизводительных U8-ядер с производительностью, аналогичной ядрам Cortex-A7x, компания какое-то время не выпускала новые ядра, а вместо этого сосредоточилась на улучшение их текущих ядер RISC-V.

Читать далее «Выпуск SiFive Core IP 21G1 улучшает обработку битов, модуль с плавающей запятой, уменьшает объем кода»