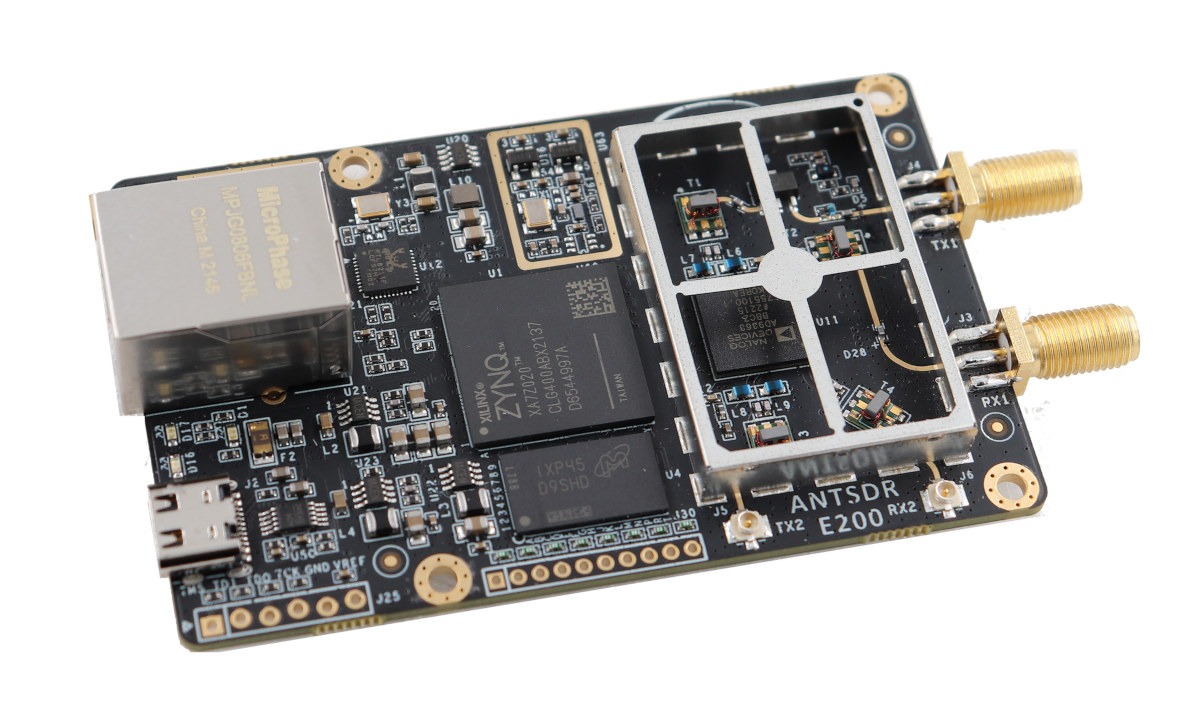

На днях мы писали о SDR-модуле uSDR M.2 на Crowd Supply, но оказалось, что на краудфандинговой платформе размещен еще один проект SDR (Software-Defined Radio) с платой AntSDR E200, оснащенной AMD Embedded Zynq 7020 SoC FPGA и набором микросхем Analog Devices AD9363 или AD9361 RF, обеспечивающих подключения Gigabit Ethernet к хосту.

Плата может работать в диапазоне 70 МГц — 6 ГГц с чипсетом AD9361 и в диапазоне 325 МГц — 3,8 ГГц с AD9363, поддерживает 2×2 MIMO с двумя антенными разъемами SMA и двумя разъемами U.FL, а также имеет возможность расширения интерфейсы для GPIO.

Читать далее «AntSDR E200 — SDR, подключенный к Gigabit Ethernet, с Xilinx Zynq SoC FPGA, поддерживает диапазон от 70 МГц до 6 ГГц (краудфандинг)»